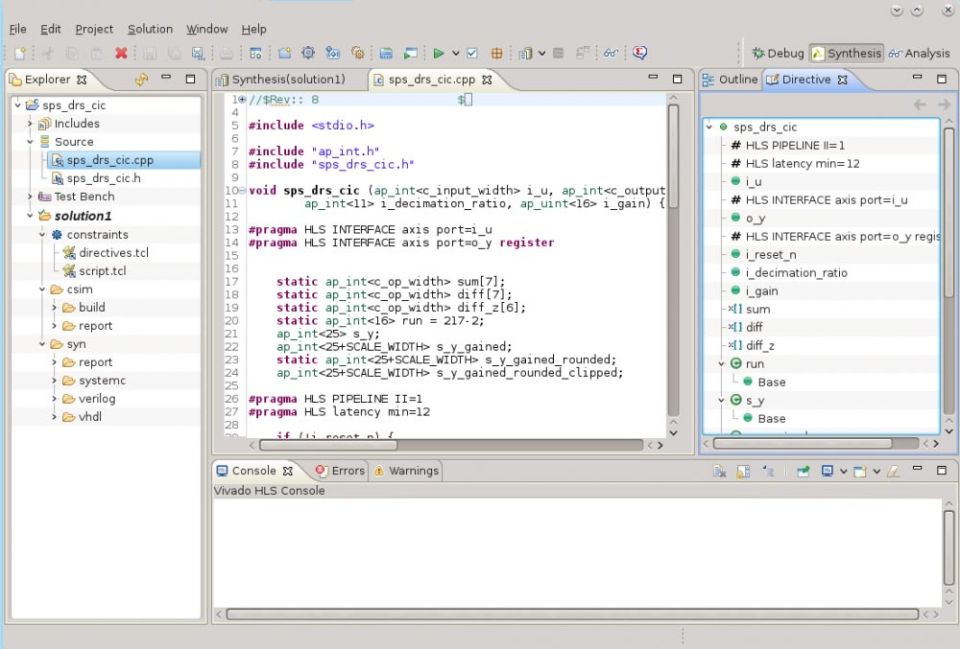

From C/C++ to FPGA

One of abaxor engineering GmbH's core competencies is the creation of FPGA designs for signal processing. As long as standard components such as FIR filters are used, we can make good use of the manufacturers' libraries. Other components, such as for:

- CIC-Filter

- IIR-Filter

- Regulator

- Non-linear calculations (Sinus, Cosinus)

- Correlations

must be created by the developer. Direct implementation in VHDL or Verilog is very complex. This is why we use High Level Synthesis in such cases. The algorithm is specified and verified in C/C++ and then translated into VHDL or Verilog with the help of an HLS compiler. This code is then used in the normal design flow.