Projects of the abaxor engineering GmbH

Ultra-Low Power Hardware for long-term machine monitoring

-

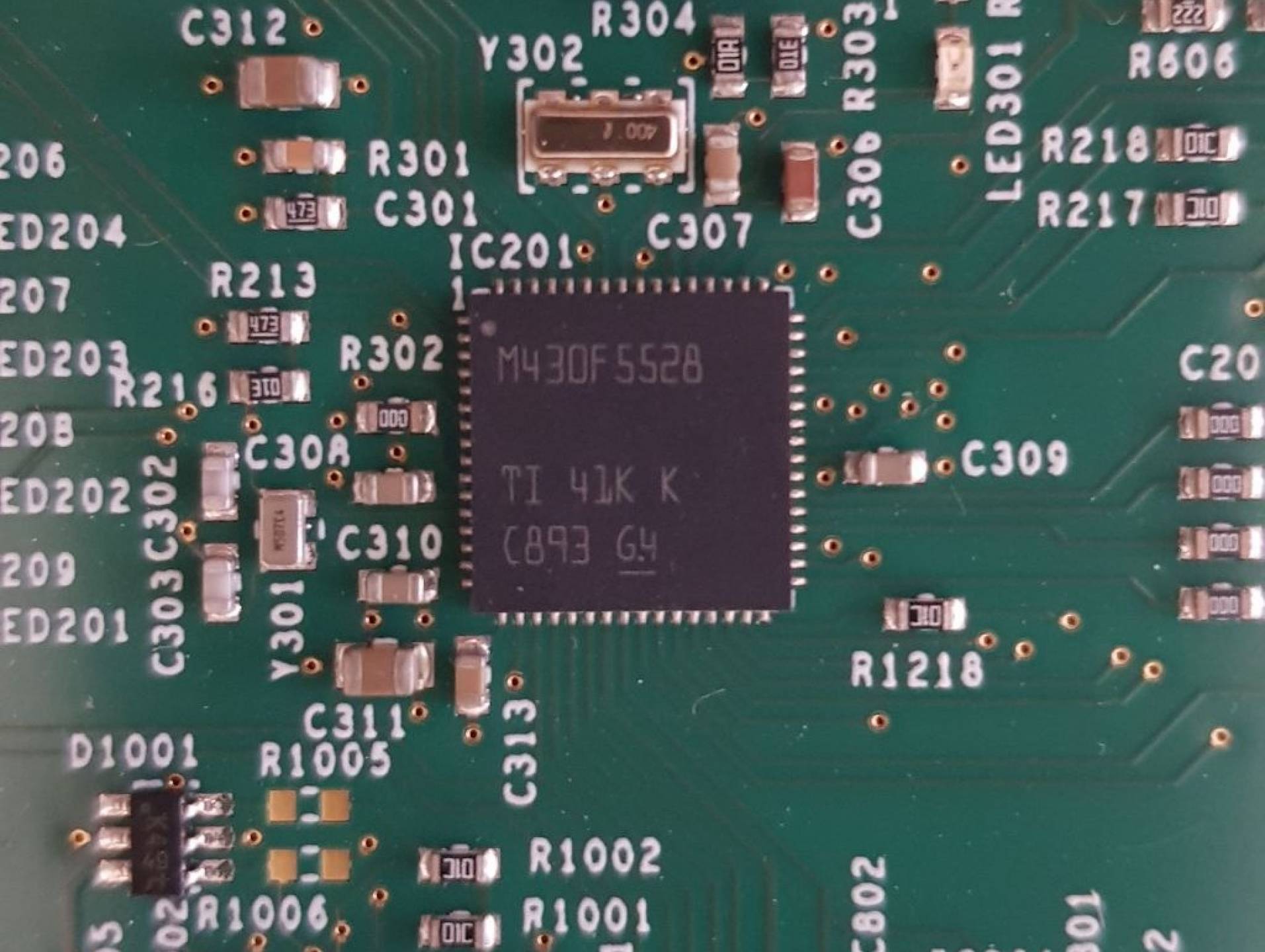

MSP430 MCU

-

machine monitoring in harsh heavy industrial environments

-

> 1 year of measurement and data recording

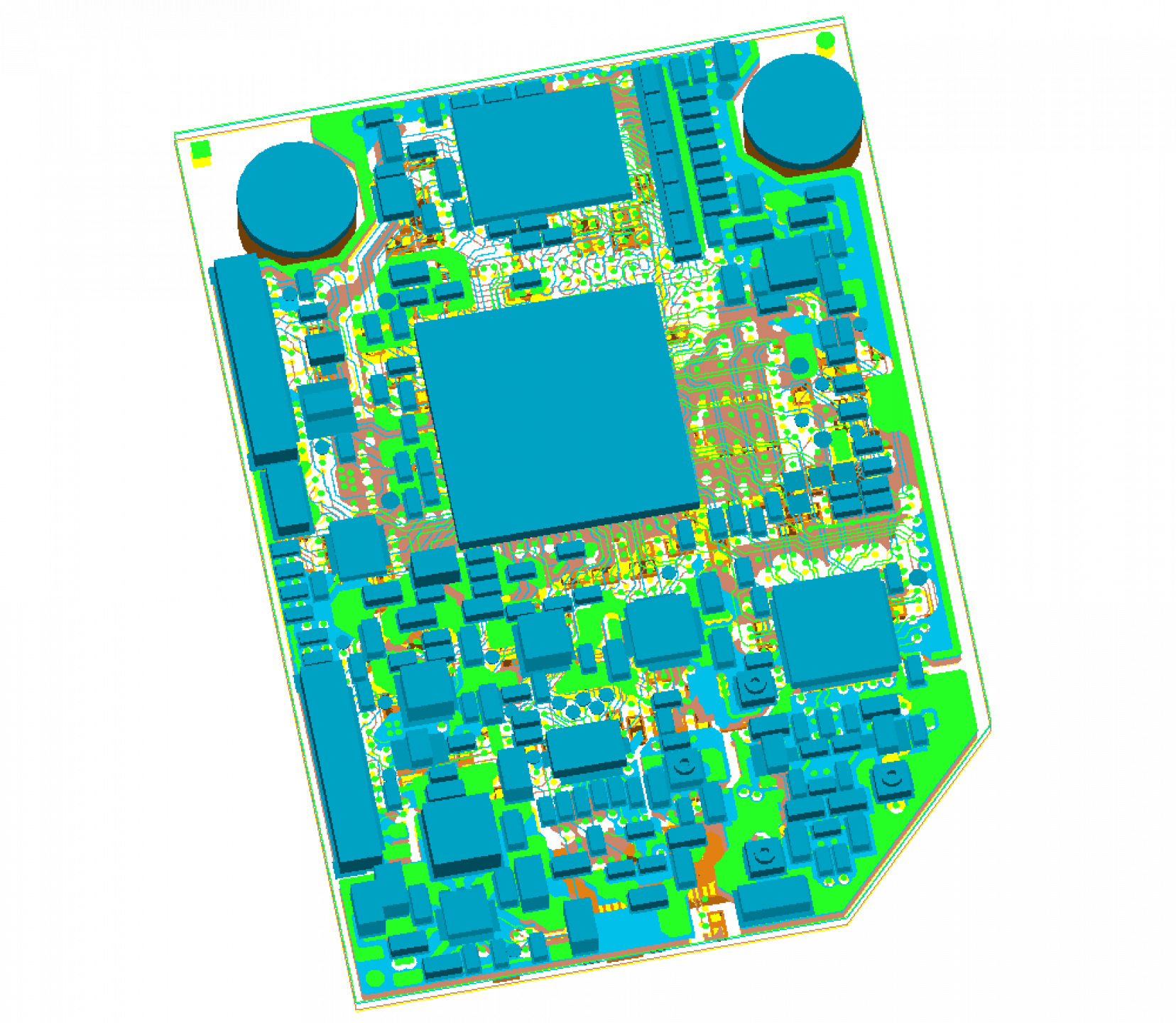

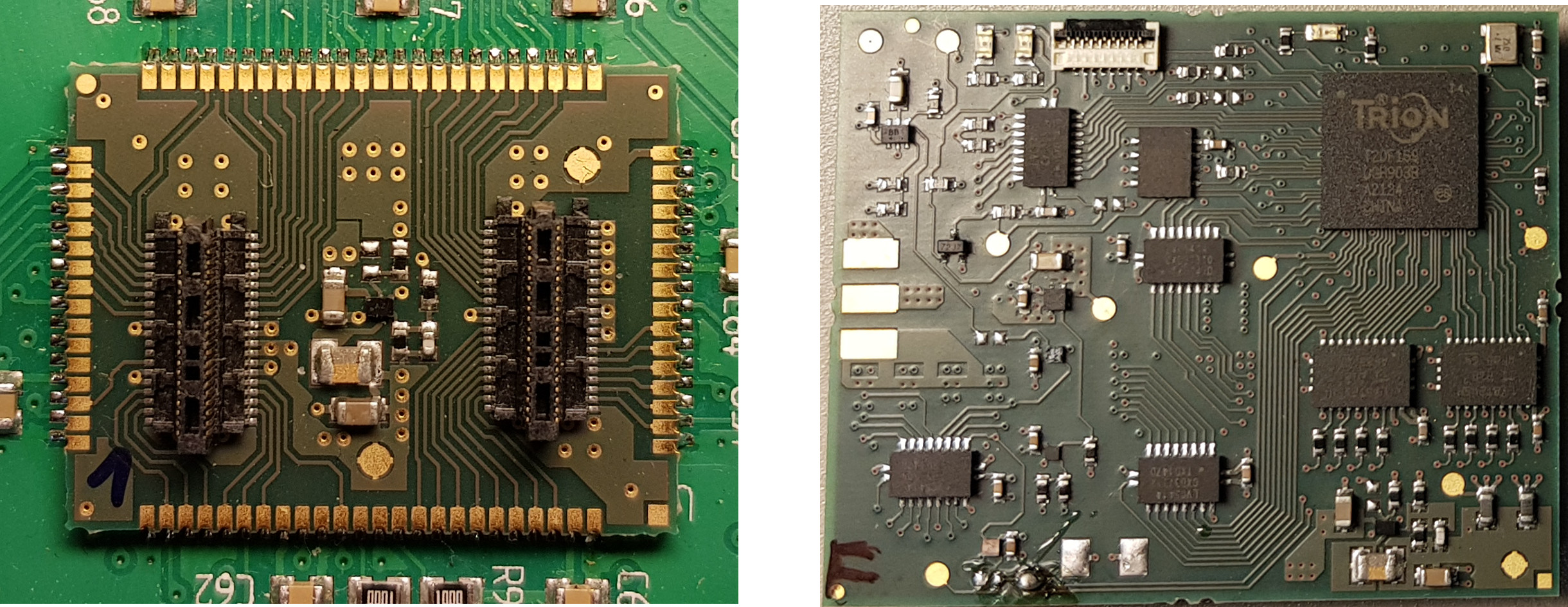

Ultrasonic data acquisition unit

-

Miniatiurized hardware (45 mm ⨯ 65 mm)

-

Efinix Trion FPGA

-

DDR3 SDRAM 128Mx8

-

ADC 12 bit, 125 MS/s

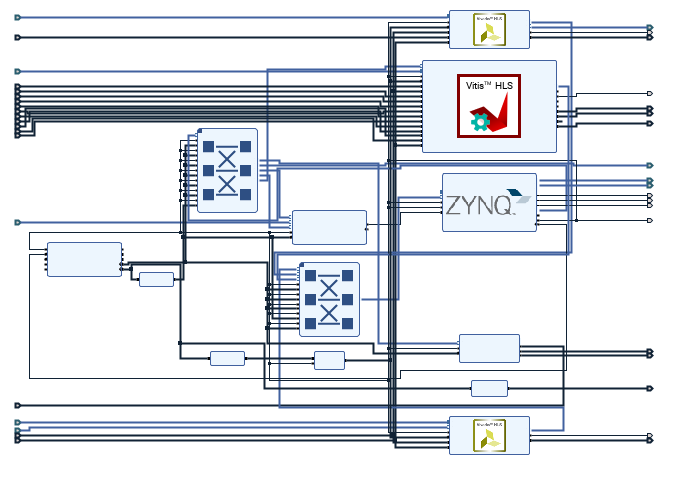

10 Gb/s Ethernet stack

- Available protocols

- ARP

- ICMP

- IPv4

- UDP Transmit

- TCP Server

- Physical Layer via MGT and SFP+ cage

- Direct Attach Cable

- LWL

- Implementation using HLS on Xilinx Artix Ultrascale+ FPGA

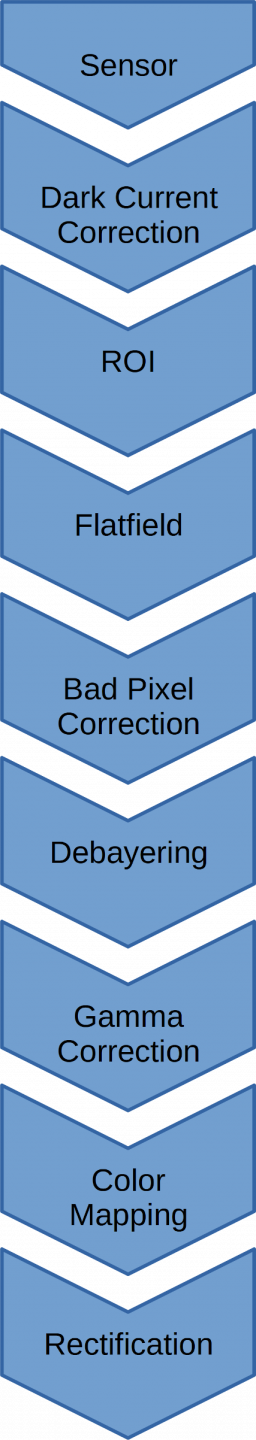

4K Image Processing

- Available functions

- Darkcurrent Correction

- ROI

- Frame Buffer

- Flatfield

- Bad Pixel Correction

- Debayering

- Color Mapping

- Gamma Correction

- Rectification

- Characteristics

- Sensor Sony IMX542

- Packet-orientated processing

- Processing of 8 pixels (24 subpixels) per step

- Implementation using HLS on Xilinx Artix Ultrascale+ FPGA

- Integration with VHDL

- Supplied with VHDL

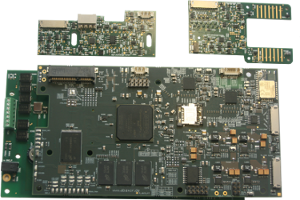

Replacement for a LC display controller using FPGA

- Two-part design

- QFP80-compatible soldering insert with connector to the logic board

- Logic board with voltage regulators, level shifter, FPGA and SPI flash

- Control of a 320x240 b/w LCD

- Emulation of the µC interface

- Efinix Trion FPGA

FPGA design, Linux kernel modules and software for a capacitive sensor

- Analysis of 12 channels

- Downsampling of the measured values to increase the resolution

- Calculation of the mass in the logic

- Live-stream of the measured values via REST-API for commissioning

- Parameterisation and output of measurement results via UDP

- Xilinx Zynq

- Regression tests for verifying functionality after software changes

- Development of software for quality assurance in production

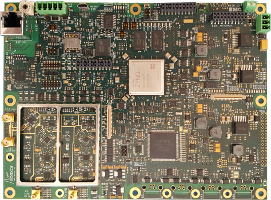

Photomultiplier analyser

- Control and analysis of photomultipliers

- Both standard and Si photomultipliers can be connected

- Digitally adjustable amplifier, bandwidth 1 GHz

- Jitter < 500 ps

- Digital resolution < 200 ps

- Xilinx Zynq FPGA

- Ethernet

- eMMC, SD-Karte, QSPI

- Debian

High-precision synchronisation unit

- Detection of the trigger with an accuracy of < 200 ps

- Generation of > 20 output signals with independently adjustable delay and a jitter < 500 ps

- Accuracy of the delay of the output signals < 100 ps

- Xilinx Zynq FPGA

- PCIe, Ethernet

- SD-Karte

- Debian

Control device for medical equipment with Altera SoC and Cyclone V FPGA

- concurrent inspection of FPGA and SoC

- ECC DDR3-SDRAM 333 MHz- 2x GBit Ethernet and LVDS for external components

- Linux operating system and custom FPGA design

- AXI master over FPGA2SDRAM bridge for SDRAM access

- AXI-LW slaves via LWHPS2FPGA bridge

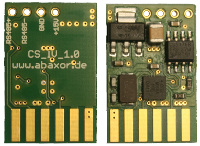

Spartan 6 module for signal processing

-

image processing and transfer via Ethernet

-

Xilinx Spartan6 LX75 FPGA

-

2x 128MiB DDR3-SDRAM 800MHz

-

1x 100MBit/s Ethernet

-

FPGA design for image processing

-

UDP/IP stack in VHDL

-

custom AXI4 masters

Control for a testing device

- HW/SW codesign

- ARM Cortex M3 (LPC1754)

- integrated display

- drive control

- One-Wire temperature sensors

Fibreoptic measuring and processing module (Fiber-Bragg-grating)

- measurement system for industrial environment

- analog signal conditioning

- data processing with Altera Cyclone V SoC

- transformer-based power supply

- data transfer over WiFi

- custom FPGA design, Linux and NIOS

- custom AXI slaves and AXI LW slaves

- CCD and SLD control

Trigger control electronics for light barrier evaluation

- Atmel ATTiny microcontroller

- USB interface

FPGA design for electronic excess-current protection

- ProASIC3 von Mikrosemi

- PCM Demodulator

- FIR Filter

- Communication per SPI

Signal processing module for external sensor

- using Altera cyclone V FPGA

- LVDS-based communication

- connectors to stack onto interface PCB

Industrial control interface component

- interface board

- Atmel AVR microcontroller

- fixture data storage

- operating hours counter

- access via RS485

Machine control device

- piezo-electric sensor inputs

- analog signal conditioning

- frequency converter controller

- user interface

- Xilinx Spartan6 FPGA with MicroBlaze softcore processor

Interface adaptor for camera

- excess voltage and inverse-polarity protection for the camera

- far range input

- RS232 interface

Additional peripherals for Infineon C167 processor

- redesign of hardware components

- advanced design of embedded software for C167

FPGA design for measurement and calculation of residual currents

- Microsemi/Actel ProASIC5 (5x)

- PCM demodulation (sinc-filter)

- FIR Filter

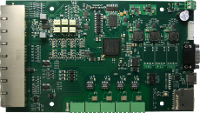

Image data capturing system

- hard- and software design

- Altera Cyclone 4 FPGA

- ARM Cortex M3

- Gigabit-Ethernet

Ultrasound measuring system to detect mechanical tension in connecting components

- stimuli with arbitrary signals up to 50 MHz

- high-sensitivity echo amplification (46dB)

- 250 MHz DA and AD conversion

- Xilinx Virtex 5 FPGA

- MicroBlaze softcore processor

- DDR-SDRAM

- Ethernet interface

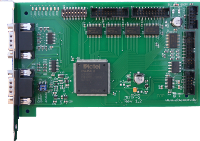

PCIe plug-in board for industrial purposes

- Xilinx Virtex 5 FPGA

- multilayer PCB

- Power PC architecture

- DDR2-SDRAM

- Ethernet interface

- running on embedded Linux

CAN interface extension for an industrial control

- Lattice ECP2M

- PCIe interface

- CAN interface

Data capturing plug-in board

- Microsemi/Actel ProASIC3

- processing of rotary encoder signal

- processing of analog 0-10V input

Laser controller for the generation of a position- and speed-dependent PWM

- MicroSemi/Actel ProASIC3

- processing of rotary encoder signal

- processing of digital inputs

FPGA design for an industrial control

- MicroSemi/Actel ProASIC3

- processing of rotary encoder signal

- processing of digital inputs

FPGA design for an image capturing device

- Lattice XP2

- capturing of images up to 3MPixels

- resolution reduction

- buffering of data

- data transfer to host processor

Image source combinator for a TFT display

- Xilinx Spartan 3A

- image capturing of 2 individual sources

- buffering

- combination into one image

- output stream to TFT display

Detection of leakage with ultrasound

- leak detection at pressure < 100mbar

- ultrasound measurement with piezo-eletric transducers, 16-channel

- analog signal conditioning

- PLC interface

Processing unit for a photon detector and counter

- jitter-free compression and transfer of APD-signals

- monitoring of photon count for safety shutdown

- individual enabling for each single APD